# Lecture Notes in Computer Science

5374

Commenced Publication in 1973

Founding and Former Series Editors:

Gerhard Goos, Juris Hartmanis, and Jan van Leeuwen

#### **Editorial Board**

David Hutchison

Lancaster University, UK

Takeo Kanade

Carnegie Mellon University, Pittsburgh, PA, USA

Josef Kittler

University of Surrey, Guildford, UK

Jon M. Kleinberg

Cornell University, Ithaca, NY, USA

Alfred Kobsa

University of California, Irvine, CA, USA

Friedemann Mattern

ETH Zurich, Switzerland

John C. Mitchell

Stanford University, CA, USA

Moni Naor

Weizmann Institute of Science, Rehovot, Israel

Oscar Nierstrasz

University of Bern, Switzerland

C. Pandu Rangan

Indian Institute of Technology, Madras, India

Bernhard Steffen

University of Dortmund, Germany

Madhu Sudan

Massachusetts Institute of Technology, MA, USA

Demetri Terzopoulos

University of California, Los Angeles, CA, USA

Doug Tygar

University of California, Berkeley, CA, USA

Gerhard Weikum

Max-Planck Institute of Computer Science, Saarbruecken, Germany

Ponnuswamy Sadayappan Manish Parashar Ramamurthy Badrinath Viktor K. Prasanna (Eds.)

# High Performance Computing -HiPC 2008

15th International Conference Bangalore, India, December 17-20, 2008 Proceedings

#### Volume Editors

Ponnuswamy Sadayappan

The Ohio State University, Department of Computer Science and Engineering 2015 Neil Avenue, Columbus, OH 43210, USA

E-mail: sadayappan.1@osu.edu

Manish Parashar

Rutgers, The State University of New Jersey Department of Electrical and Computer Engineering 94 Brett Road, Piscataway, NJ 08854, USA, E-mail: parashar@caip.rutgers.edu

Ramamurthy Badrinath Hewlett-Packard ISO, Sy 192 Whitefield Road, Mahadevapura Post, Bangalore 560048, India E-mail: ramamurthy.badrinath@hp.com

Viktor K. Prasanna University of Southern California, Department of Electrical Engineering Los Angeles, CA 90089-2562, USA E-mail: prasanna@usc.edu

Library of Congress Control Number: 2008940427

CR Subject Classification (1998): B.2.4, D.1, C.1, F.1, G.1

LNCS Sublibrary: SL 1 – Theoretical Computer Science and General Issues

ISSN 0302-9743

ISBN-10 3-540-89893-X Springer Berlin Heidelberg New York ISBN-13 978-3-540-89893-1 Springer Berlin Heidelberg New York

This work is subject to copyright. All rights are reserved, whether the whole or part of the material is concerned, specifically the rights of translation, reprinting, re-use of illustrations, recitation, broadcasting, reproduction on microfilms or in any other way, and storage in data banks. Duplication of this publication or parts thereof is permitted only under the provisions of the German Copyright Law of September 9, 1965, in its current version, and permission for use must always be obtained from Springer. Violations are liable to prosecution under the German Copyright Law.

Springer is a part of Springer Science+Business Media

springer.com

© Springer-Verlag Berlin Heidelberg 2008 Printed in Germany

Typesetting: Camera-ready by author, data conversion by Scientific Publishing Services, Chennai, India Printed on acid-free paper SPIN: 12577897 06/3180 5 4 3 2 1 0

# Message from the Program Chair

Welcome to the 15th International Conference on High Performance Computing (HiPC 2008), held at Bangaluru (formerly called Bangalore), India. Features at this year's conference included a single-track program with 46 technical papers selected from 317 submissions, four keynote talks by renowned experts from academia, two tutorials from industry, five workshops, a student research symposium, and a user/industry symposium.

As in recent years, a large number of technical papers were submitted for consideration, covering six topic areas of focus: algorithms, applications, architecture, communication networks, mobile/sensor computing, and systems software. In reviewing the 317 submissions, we used a two-phase approach as done over the last few years with HiPC. A first screening pass was made through all papers by the area Vice Chairs to identify papers that were clearly out of scope for the conference, either because the topic did not fit the conference or the paper was of a survey nature, without original research content. After the first pass, the remaining 285 submissions were reviewed, seeking at least three reviews from Program Committee members. A number of external reviewers also provided reviews for papers. A total of 978 reviews were obtained for the papers. For papers with significantly differing opinions among Program Committee members, e-mail discussions were used to find consensus. Finally 46 papers were selected for presentation in 8 sessions.

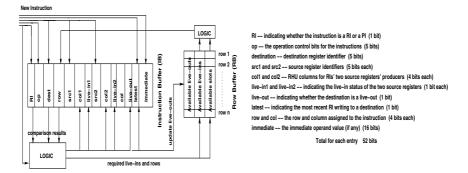

One outstanding paper was selected for the best paper award. Each area Vice Chair first nominated one or two of the best papers from their area. These papers and their reviews were studied by the Vice Chairs, who then made their recommendations for the best paper award. Based on the recommendations from the Vice Chairs, the paper "Scalable Multi-cores with Improved Per-core Performance Using Off-the-Critical Path Reconfigurable Hardware," authored by Tameesh Suri and Aneesh Aggarwal, was selected for the best paper award.

This year's program featured keynote presentations from four distinguished speakers: Wolfgang Gentzsch on the European distributed supercomputing infrastructure, David Peleg on networked computers, Mary Wheeler on a computational environment for subsurface modeling, and Laxmikant Kale on the "the excitement in parallel computing."

The quality of the technical program is critically dependent on the efforts of the Program Committee members in providing reviews for the submitted papers. I thank the 103 members of this year's Program Committee. The assignment of papers to members of the Program Committee was managed by the area Vice Chairs. I was extremely fortunate to work with dedicated Vice Chairs. The Vice Chairs were David Bader (Algorithms), Alan Sussman (Applications), David Kaeli and Martin Schulz (Architecture), José de Souza (Communication Networks), Chen-Khong Tham (Mobile and Sensor Computing), and Cho-Li Wang (Systems Software). I am very grateful to them for their hard work in handling the reviewing within their areas and their significant contributions

at the distributed virtual Program Committee meeting. Each paper's review recommendations were carefully checked for consistency; in many instances, the Vice Chairs read the papers themselves when the reviews did not seem sufficient to make a decision.

Throughout the reviewing process, I received a tremendous amount of help and advice from General Co-chair Manish Parashar, Steering Chair Viktor Prasanna, and last year's Program Chair Srinivas Aluru; I am very grateful to them. My thanks also go to the Publications Chair Sushil Prasad for his outstanding efforts in putting the proceedings together. Finally, I thank all the authors for their contributions to a high-quality technical program. I wish all the attendees a very enjoyable and informative meeting.

December 2008 P. Sadayappan

# Message from the General Co-chairs and the Vice General Co-chairs

On behalf of the organizers of the 15th International Conference on High-Performance Computing (HiPC), it is our pleasure to present these proceedings and we hope you will find them exciting and rewarding.

The HiPC call for papers, once again, received an overwhelming response, attracting 317 submissions from 27 countries. P. Sadayappan, the Program Chair, and the Program Committee worked with remarkable dedication to put together an outstanding technical program consisting of the 46 papers that appear in these proceedings.

Several events, complementing this strong technical program, made HiPC 2008 a special and exciting meeting. As in previous years, the HiPC 2008 keynotes were presented by internationally renowned researchers. HiPC 2008 also featured a full-day student research symposium prior to the main conference, which consisted of presentations and posters by students highlighting their research. The conference once again had an industry and user symposium focused on "High-Performance Computing Technologies, Applications and Experience," which ran in parallel to the main track, to bring together the users and providers of HPC. This symposium and the main conference came together for a special plenary panel on "Cloud Computing." There were several industry and research exhibits complementing the symposium and the conference main track. The meeting was preceded by a set of tutorials and workshops highlighting new and emerging aspects of the field.

Arranging an exciting meeting with a high-quality technical program is easy when one is working with an excellent and dedicated team and can build on the practices and levels of excellence established by a quality research community. HiPC 2008 would not have been possible without the tremendous efforts of the many volunteers. We would like to acknowledge the critical contributions of each one.

We would like to thank P. Sadayappan, Program Chair, and the Program Committee for their efforts in assembling such an excellent program, and the authors who submitted the high-quality manuscripts from which that program was selected. We would also like to thank the presenters of the keynotes, posters and tutorials, the organizers of the workshops, and all the participants, who completed the program.

We would specially like to thank Viktor Prasanna, Chair of the HiPC Steering Committee, for his leadership, sage guidance, and untiring dedication, which have been key to the continued success of the conference. We would also like to welcome our new volunteers to the team - your efforts are critical to the continued success of this conference. Finally, we would like to gratefully acknowledge our academic and industry sponsors including IEEE Computer Society, ACM SIGARCH, Infosys, DELL, NetApp, Intel, HP, IBM, Yahoo!, Cray and Mellanox.

December 2008

Manish Parashar Ramamurthy Badrinath Rajendra V. Boppana Rajeev Muralidhar

# Message from the Steering Chair

It is my pleasure to welcome you to the proceedings of the 15th International Conference on High Performance Computing and to Bengaluru, the leading center of IT activity in India.

My "thank you" goes to many volunteers whose dedicated effort over the past year has made this conference a successful endeavor. P. Sadayappan, our Program Chair, has done an outstanding job in putting together an excellent technical program. I am indebted to him for his thorough evaluation of the submitted manuscripts and his relentless efforts to further improve the quality of the technical program. Manish Parashar and Ramamurthy Badrinath as General Co-chairs provided the leadership in resolving numerous meeting-related issues and putting together the overall program including the workshops and tutorials. They were ably assisted by Rajeev Muralidhar, Vice General Co-chair. The industry track was coordinated by Rama Govindaraju with assistance from Frank Baetke and Santosh Sreenivasan. We have several continuing as well as new workshops. These workshops were coordinated by Manimaran Govindarasu. The website was maintained by Yinglong Xia. Animesh Pathak acted as the Production Chair overseeing various activities related to the Web and creating publicity materials. The Student Research Symposium was organized by Ashok Srinivasan and Rajeev Thakur. Rajeev Sivaram assisted us with the tutorials. The local arrangements were handled by C. Kalyana Krishna and Raghavendra Buddi. Sushil Prasad interfaced with the authors and Springer to bring out the proceedings. Manisha Gajbe and Ashok Srinivasan handled the publicity for us. Sally Jelinek and Jyothsna Kasthurirengan acted as the Registration Co-chairs. Ajay Gupta and Thondiyil Venugopalan were in charge of the meeting finances. Sumam David and Madhusudan Govindaraju administered the student scholarships.

I would like to thank all our volunteers for their tireless efforts. The meeting would not be possible without the enthusiastic effort and commitment of these individuals.

Major financial support for the meeting was provided by several leading IT companies and multinationals operating in India. I would like to acknowledge the following individuals and their organizations for their support:

- N.R. Narayana Murthy, Infosys

- Kris Gopalakrishnan, Infosys

- David Ford, NetApp

- Siddhartha Nandi, NetApp

- B. Rudramuni, Dell India

- Ramesh Rajagopalan, Dell India

- Reza Rooholamini, Dell

- V. Sridhar, Satyam

- Prabhakar Raghavan, Yahoo! Inc.

- Arun Ramanujapuram, Yahoo! India R&D

- Vittal Kini, Intel Research, India

#### X Preface

- Biswadeep Chatterjee, Intel Research, India

- Venkat Natarajan, Intel Research, India

- Manish Gupta, IBM India

- Dinkar Sitaram, HP India

- Faisal Paul, HP India

- Venkat Ramana, Hinditron Infosystems

December 2008 Viktor K. Prasanna

# **Conference Organization**

#### **General Co-chairs**

Manish Parashar Rutgers University, USA

Ramamurthy Badrinath HP, India

#### Vice General Co-chairs

Rajeev Muralidhar Intel, India

Rajendra V. Boppana University of Texas at San Antonio, USA

**Program Chair**

P. Sadayappan Ohio State University, USA

#### **Program Vice Chairs**

Algorithms

David Bader Georgia Institute of Technology, USA

**Applications**

Alan Sussman University of Maryland, USA

Architecture

David Kaeli Northeastern University, USA

Martin Schulz Lawrence Livermore Laboratory, USA

**Communication Networks**

José Neuman de Souza Federal University of Ceará, Brazil

Mobile and Sensor Computing

Chen-K Tham National University of Singapore

**Systems Software**

Cho-li Wang Hong Kong University

**Steering Chair**

Viktor K. Prasanna University of Southern California, USA

#### **Workshops Chair**

Manimaran Govindarasu Iowa State University, USA

# **Student Research Symposium Co-chairs**

Ashok Srinivasan Florida State University, USA Rajeev Thakur Argonne National Laboratory, USA

#### **Tutorials Chair**

Rajeev Sivaram Google, USA

#### **Industry Liaison Chair**

Rama K. Govindaraju Google, USA

#### **HiPC User Symposium Co-chairs**

Rama K. Govindaraju Google, USA Santosh Sreenivasan Talentain, India

#### **Cyber Co-chairs**

Ananth Narayan Intel, India

Kamesh Madduri Georgia Institute for Technology, USA Yinglong Xia University of Southern California, USA

#### Finance Co-chairs

Ajay Gupta Western Michigan University, USA

Thondiyil Venugopalan India

#### **Local Coordination Co-chairs**

Kalyana Krishna Talentain, India Raghavendra Buddi NetApp, India

#### **Production Chair**

Animesh Pathak University of Southern California, USA

#### **Publications Chair**

Sushil K. Prasad Georgia State University, USA

#### **Publicity Co-chairs**

Ashok Srinivasan Florida State University, USA

Manisha Gajbe Georgia Institute of Technology, USA

#### **Registration Co-chairs**

Sally Jelinek Electronics Design Associates, USA

Jyothsna Kasthurirengan Fiberlink, India

#### **Scholarships Co-chairs**

Sumam David NITK, India

Madhusudhan Govindaraju SUNY Binghamton, USA

#### **Steering Committee**

Steering Committee 2008 membership also includes the General Co-chairs, Program Chairs and Vice General Co-chairs from 2007 and 2008.

P. Anandan Microsoft Research, India

David A. Bader Georgia Institute of Technology, USA

Ramamurthy Badrinath HP, India

Rudramuni B. Dell India R&D, Bangalore, India

Frank Baetke HP, USA Anirban Chakrabarti Infosys, India

R. Govindarajan Indian Institute of Science, India

Harish Grama IBM, India

Manish Gupta India Systems and Technology Lab, IBM, India

Vittal Kini Intel, India

Ashwini Nanda Computational Research Lab., India

Viktor K. Prasanna University of Southern California, USA (Chair)

Venkat Ramana Cray-Hinditron, India

Sartaj Sahni University of Florida, USA

Santosh Sreenivasan Talentain Technologies, India

V. Sridhar Satyam Computer Services Ltd., India

Harrick M. Vin Tata Research, Development & Design Center, Pune,

India

#### **Program Committee**

#### Algorithms

Srinivas Aluru Iowa State University, USA

Guojing Cong IBM T.J. Watson Research Center, USA

Camil Demetrescu University of Rome, Italy

#### XIV Organization

Devdatt Dubhashi Chalmers University of Technology, Sweden

Matteo Frigo Cilk Arts, USA

Anshul Gupta IBM T.J. Watson Research Center, USA

Klaus Jansen University of Kiel, Germany

Jeremy Johnson Drexel University, USA

Christos Kaklamanis University of Patras, Greece

Ananth Kalyanaraman Washington State University, USA

Jesper Larsson Traeff NEC Laboratories, Europe

Kamesh Madduri Georgia Institute of Technology, USA

Greg Malewicz Google, USA Madhav Marathe Virginia Tech., USA

Geppino Pucci University of Padova, Italy

Sandeep Sen Indian Institute of Technology, Delhi, India

Christian Sohler University of Paderborn, Germany

Philippas Tsigas Chalmers University of Technology, Sweden

Tiffani Williams Texas A & M University, USA

#### **Applications**

Henrique Andrade IBM T.J. Watson Research Center, USA

Umit Catalyurek Ohio State University, USA

Nikos Chrisochoides College of William and Mary, USA

I-Hsin Chung IBM T.J. Watson Research Center, USA

Lois Curfman McInnes Argonne National Laboratory, USA

Jens Gustedt LORIA, France

Fumihiko Ino Osaka University, Japan

P.J. Narayanan Indian Institute of Information Technology,

Hyderabad, India

Daniel S. Katz

Louisiana State University, USA

Jim Kohl

Oak Ridge National Laboratory, USA

Kalyan Kumaran

Argonne National Laboratory, USA

Gary Kumfert Lawrence Livermore National Laboratory, USA

Steve Parker University of Utah, USA

Padma Raghavan Pennsylvania State University, USA

Ramesh Rajagopalan Dell, India

Satish Vadhiyar Indian Institute of Science, India Yao Zheng Zhejiang University, China

#### Architecture

Rosa Badia Barcelona Supercomputer Center, Spain

Rajeev Balasubramonian University of Utah, USA

Anasua Bhowmik AMD, India

Antonio Gonzalez Intel Barcelona Research Center, Spain

Ananth Grama Purdue University, USA Kim Hazelwood University of Virginia, USA

Helen Karatza Aristotle University of Thessaloniki, Greece

Sriram Krishnamoorthy Pacific Northwest National Laboratory, USA

Hrishi Murukkathampoondi AMD, India

Ranjani Parthasarathy Anna University, India Srinivasan Parthasarathy Ohio State University, USA

Rodric Rabbah IBM T.J. Watson Research Center, USA

J. Ramanujam

Partha Ranganathan

Pat Teller

Ramon Canal

Timothy Pinkston

Louisiana State University, USA

HP Research Laboratories, USA

University of Texas at El Paso, USA

Universitat Politécnica de Catalunya, Spain

University of Southern California, USA

Peter Varman Rice University, USA

Youfeng Wu Intel, USA

#### **Communication Networks**

Pavan Balaji Argonne National Laboratory, USA

Rajendra Bopanna University of Texas at San Antonio, USA

Ron Brightwell Sandia National Laboratory, USA

Rajkumar Kettimuthu Argonne National Laboratory, USA

John Kim Northwestern University, USA

Jiuxing Liu IBM T.J. Watson Research Center, USA

David Lowenthal University of Georgia, USA Amith Mamidala Ohio State University, USA

Jarek Nieplocha Pacific Northwest National Laboratory, USA

Thirumale Niranjan NetApp Research, India

Fabrizio Petrini IBM T.J. Watson Research Center, USA

Sayantan Sur IBM T.J. Watson Research Center, USA

Vinod Tipparaju Pacific Northwest National Laboratory, USA

Weikuan Yu Oak Ridge National Laboratory, USA

Xin Yuan Florida State University, USA

#### **Mobile and Sensor Computing**

Kevin Almeroth University of California at Santa Barbara, USA Twan Basten Technical University of Eindhoven, The Netherlands

Mun-Choon Chan National University of Singapore, Singapore

Eylem Ekici Ohio State University, USA

Polly Huang National Taiwan University, Taiwan

Vana Kalogeraki University of California at Riverside, USA

Peng-Yong Kong Institute for Infocomm Research, Singapore

Victor Leung University of British Columbia, Canada

Jun Luo University of Waterloo, Canada

Hoon-Tong Ngin Infocomm Development Authority, Singapore

Marimuthu Palaniswami University of Melbourne, Australia

Karim Seada Nokia Research, USA

Winston Seah Institute for Infocomm Research, Singapore

#### XVI Organization

Vikram Srinivasan Alcatel-Lucent Bell Labs, India

Wendong Xiao Institute for Infocomm Research, Singapore Athanasios Vasilakos University of Western Macedonia, Greece

#### Systems Software

Rajkumar Buyya University of Melbourne, Australia Yeh-Ching Chung National Tsing Hua University, Taiwan

Bronis De Supinski Lawrence Livermore National Laboratory, USA

R. Govindarajan Indian Institute of Science, India

Jaejin Lee Seoul National University, Korea

Kuan-Ching Li Providence University, Taiwan

Philippe Navaux Federal University of Rio Grande do Sul, Brazil

Lawrence Rauchwerger Texas A & M University, USA

Vijay A. Saraswat IBM T.J. Watson Research Center, USA

Henk Sips Delft University of Technology, The Netherlands

Ninghui Sun Chinese Academy of Sciences, China

Yoshio Tanaka National Inst. of Advanced Industrial Science and

Technology, Japan

Putchong Uthayopas Kasetsart University, Thailand

Richard Vuduc Georgia Institute of Technology, USA Laurence T. Yang St. Francis Xavier University, Canada

#### Workshops

#### Workshop on Grid and Utility Computing

#### **Organizers**

Anirban Chakrabarti Infosys Technologies, India

Shubhashis Sengupta Oracle, India

#### Workshop on Service-Oriented Engineering and Optimizations

#### **Organizers**

Badrinath Ramamurthy HP India Geetha Manjunath HP India

#### **Workshop on Next-Generation Wireless Networks**

#### **Organizers**

B. Prabakaran University of Texas, Dallas, USA

S. Dharmaraja Indian Institute of Technology, Delhi, India

#### High-Performance FPGA/Reconfigurable Computing

#### **Organizers**

Tirumale Ramesh The Boeing Company, USA Venkata Ramana Hinditron-CRAY, India

Mrugesh Gajjar

#### Cooling of HiPC Systems: Why Should Computer Scientists Care?

#### **Organizers**

Venkat Natarajan (Chair) Intel Corporation Anand Deshpande (Co-chair) Intel Corporation

#### **Tutorials**

#### **High-Performance Computing with CUDA**

Sanjiv Satoor NVIDIA corp Punit Kishore NVIDIA corp

# **Hadoop – Delivering Petabyte-Scale Computing and Storage on Commodity Hardware**

Yahoo Bangalore Cloud

Computing Team Yahoo, India

#### **List of Reviewers**

Virat Agarwal

In addition to the PC members, the following colleagues provided reviews for HiPC 2008 papers. Their help is gratefully acknowledged.

Marcia Cera

| Gagan Agrawal           | Girish Chandramohan | Anilton Garcia        |

|-------------------------|---------------------|-----------------------|

| Rui Aguiar              | Chin-Chen Chang     | Yu Ge                 |

| Gheorge Almasi          | Bin Chen            | Stephane Genaud       |

| Alexander van Amesfoort | Jianxia Chen        | Amol Ghoting          |

| Chee Ang                | Min Chen            | Enric Gibert          |

| Paolo Bertasi           | Raphael Coeffic     | William Giozza        |

| Vandy Berten            | Luis Costa          | Antonio Gomes         |

| Elisa Bertino           | Pilu Crescenzi      | Danielo Gomes         |

| Cristian Bertocco       | Chirag Dave         | Jose Gonzalez         |

| Mauro Bianco            | Sheng Di            | Raju Gottumukkala     |

| Karima Boudaoud         | Jiun-Hung Ding      | Manimaran Govindarasu |

| Steven Brandt           | Evgueni Dodonov     | Helio Guardia         |

Francisco Brasileiro Kshitij Doshi John Gunnels **Darius Buntinas** Yew Fai Wong Mingding Han R.C. Hansdah Carlo Fantozzi R. Hansdah Jason C. Hung Paulo Fernandes Ramin Hekmat Ken C.K. Tsang Marcial Fernandez Kevin Ho Mark C.M. Tsang Andrei Formiga Roy Ho Luca Foschini Qiong Cai Sai Ho Wong Enrique Carrera Miguel Franklin de Castro Tuan Hoang Joaquim Celestino Mario Freire Meng-Ju Hsieh Chin-Jung Hsu

Haoyu Hu

Kuo-Chan Huang

Jason Hung

Andrei Hutanu

Borhan Jalaeian

Shantenu Jha

Yingyin Jiang

Qing Jun Zhang

Francisco Junior Carlos Kamienski Rodrigo Kassick Ian Kelley

Gaurav Khanna Hyesoon Kim Joohyun Kim Kok Kiong Yap David Koppelman

Ka Kui Ma

Archit Kulshrestha Benjamin Lee Arnaud Legrand

Tieyan Li Wei Lih Lim Meng-How Lim Shih-Hsiang Lo

Tie Luo

Nicolas Maillard Gianluca Maiolini Konstantin Makarychev

Konstantin Makarychev R. Manikantan Joberto Martins Lorne Mason

Francisco Massetto Collin McCurdy Rodrigo Mello Lucas Mello Schnorr Luciano Mendes Hashim Mohamed Carlos Molina

Gregory Mounie Y.N. Srikant Ghasem Shirazi

Soumitra Nandy Siyaramakrishnan Narayanan

Lee-Ling Ong Sreepathi Pai Thomas Panas Qixiang Pang Ioannis Papadopoulos

Xiaoming Peng Maikel Pennings Angelo Perkusich Marcelo Pias

Sriram Pemmaraju

Hwee Pink Tan Dario Pompili Monica Py

R. Vasudha Kaushik Rajan Easwaran Raman Rodrigo Righi Eduardo Rocha Philip Roth Lifeng Sang

Aldri Santos Andre Santos Abhinav Sarje Daniele Scarpazza

Srinivasan Seetharaman Aiyampalayam Shanthi Jeonghee Shin

Zheng Shou Kang

Chee Shin Yeo

Francesco Silvestri Gurmeet Singh Prasun Sinha Tim Smith Wee-Seng Soh Joo-Han Song Francois Spies

K.N. Sridhar Mukundan Sridharan Y.N. Srikant

Michael Stanton

Wen Su Xu Su

Dharmashankar Subramanian Karthik Subramanian

Peng Sun

Sayantan Sur

Sai Susarla

Le Sy Quoc

Alex Tabbal

Eddie Tan

Hwee-Xian Tan

Gabriel Tanase

Shao Tao

Mukarram Tariq Joseph Teo James Teresco

Matthew Thazhuthaveetil

Nathan Thomas King Tin Lam Srikanta Tirthapura Andrei Tolstikov Ken Tsang Mark Tsang

David Tung Chong Wong

Abhishek Udupa Alvin Valera Ana Varbanescu Srikumar Venugopal Jakob Verbeek Javier Verdu Francesco Versaci Stephane Vialle

Venkatram Vishwanath

Andy Wang Chien-Min Wang Jun Wang Wei Wang

Tien-Hsiung Weng Marek Wieczorek Chih-Ying Wu Jan-Jan Wu Haiyong Xie Ai Xin

Chao-Tung Yang Laurence Yang Yu Yang

Yu Yang Serhan Yarkan Wai-Leong Yeow Hao Yu Yan Zhang Wenjie Zeng Zizhan Zheng Mingze Zhang Hu Zheng Qing Jiazheng Zhou Artur Ziviani

#### Table of Contents

**Keynote Addresses**

| Extreme Computing on the Distributed European Infrastructure for Supercomputing Applications – DEISA                                                                               | 1  |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| Towards Networked Computers: What Can Be Learned from Distributed Computing?                                                                                                       | 2  |

| $ \begin{array}{c} \text{Computational Environments for Coupling Multiphase Flow, Transport,} \\ \text{and Mechanics in Porous Media.} \\ \text{\it Mary F. Wheeler} \end{array} $ | 3  |

| The Excitement in Parallel Computing                                                                                                                                               | 5  |

| Session I: Performance Optimization                                                                                                                                                |    |

| Improving Performance of Digest Caches in Network Processors  Girish Chandramohan and Govindarajan Ramaswamy                                                                       | 6  |

| Optimization of BLAS on the Cell Processor                                                                                                                                         | 18 |

| Fine Tuning Matrix Multiplications on Multicore                                                                                                                                    | 30 |

|                                                                                                                                                                                    |    |

#

| Efficient PDM Sorting Algorithms                                                                                                                                                                  | 97  |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| Accelerating Cone Beam Reconstruction Using the CUDA-Enabled GPU                                                                                                                                  | 108 |

| Yusuke Okitsu, Fumihiko Ino, and Kenichi Hagihara                                                                                                                                                 |     |

| Improving the Performance of Tensor Matrix Vector Multiplication in Cumulative Reaction Probability Based Quantum Chemistry Codes Dinesh Kaushik, William Gropp, Michael Minkoff, and Barry Smith | 120 |

| Experimental Evaluation of Molecular Dynamics Simulations on                                                                                                                                      |     |

| Multi-core Systems                                                                                                                                                                                | 131 |

| Parsing XML Using Parallel Traversal of Streaming Trees Yinfei Pan, Ying Zhang, and Kenneth Chiu                                                                                                  | 142 |

| Session III: Scheduling and Resource Management                                                                                                                                                   |     |

| Performance Analysis of Multiple Site Resource Provisioning: Effects of the Precision of Availability Information                                                                                 | 157 |

| An Open Computing Resource Management Framework for Real-Time Computing                                                                                                                           | 169 |

| A Load Aware Channel Assignment and Link Scheduling Algorithm for Multi-channel Multi-radio Wireless Mesh Networks                                                                                | 183 |

| Multi-round Real-Time Divisible Load Scheduling for Clusters                                                                                                                                      | 196 |

| Energy-Efficient Dynamic Scheduling on Parallel Machines                                                                                                                                          | 208 |

| A Service-Oriented Priority-Based Resource Scheduling Scheme for Virtualized Utility Computing                                                                                                    | 220 |

| Session IV: Sensor Networks                                                                                                                                                                       |     |

| Scalable Processing of Spatial Alarms                                                                                                                                                             | 232 |

| Networks                                                                                                                                             | 245 |

|------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| Kiran Rachuri, A. Antony Franklin, and C. Siva Ram Murthy                                                                                            |     |

| An Energy-Balanced Task Scheduling Heuristic for Heterogeneous Wireless Sensor Networks                                                              | 257 |

| Energy Efficient Distributed Algorithms for Sensor Target Coverage Based on Properties of an Optimal Schedule                                        | 269 |

| In-Network Data Estimation for Sensor-Driven Scientific Applications                                                                                 | 282 |

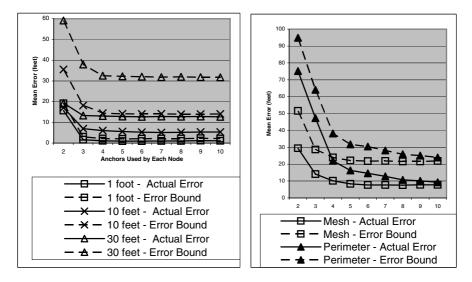

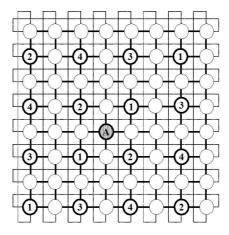

| Localization in Ad Hoc and Sensor Wireless Networks with Bounded Errors                                                                              | 295 |

| Session V: Energy-Aware Computing                                                                                                                    |     |

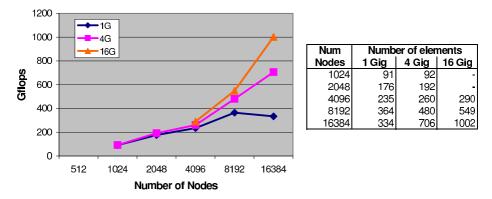

| Optimization of Fast Fourier Transforms on the Blue Gene/L Supercomputer                                                                             | 309 |

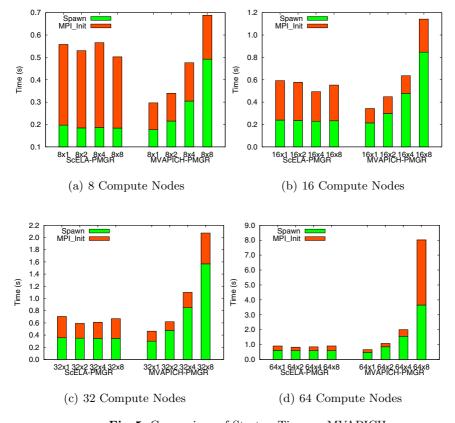

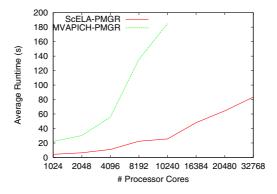

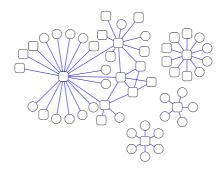

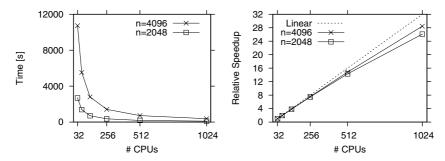

| ScELA: Scalable and Extensible Launching Architecture for Clusters Jaidev K. Sridhar, Matthew J. Koop, Jonathan L. Perkins, and Dhabaleswar K. Panda | 323 |

| Parallel Information Theory Based Construction of Gene Regulatory Networks                                                                           | 336 |

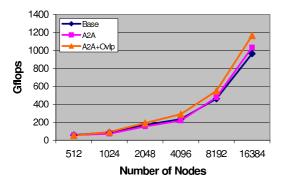

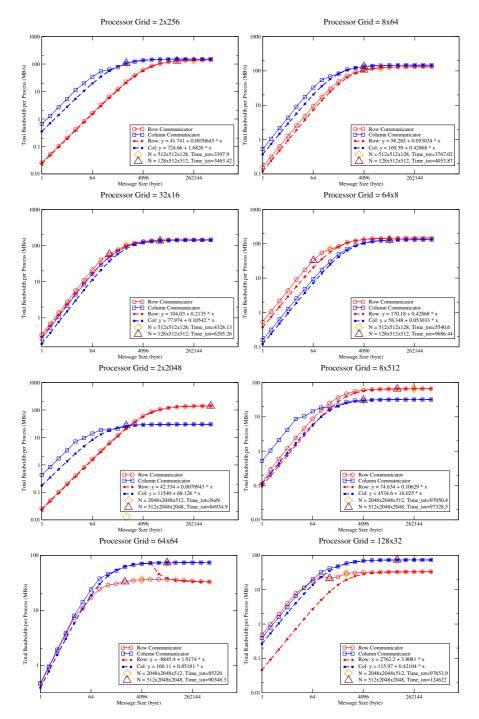

| Communication Analysis of Parallel 3D FFT for Flat Cartesian Meshes on Large Blue Gene Systems                                                       | 350 |

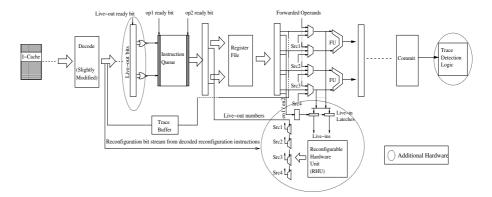

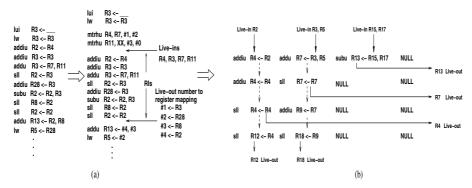

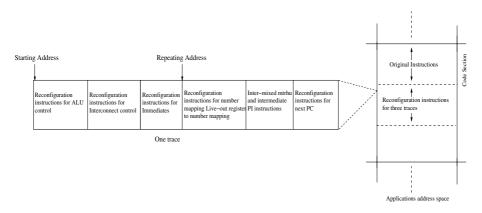

| Scalable Multi-cores with Improved Per-core Performance Using Off-the-critical Path Reconfigurable Hardware                                          | 365 |

| Session VI: Distributed Algorithms                                                                                                                   |     |

| TrustCode: P2P Reputation-Based Trust Management Using Network Coding                                                                                | 378 |

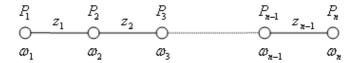

| Unaware Scheduling Strategy for Processing Divisible Loads on Distributed Linear Daisy Chain Networks           | 390 |

|-----------------------------------------------------------------------------------------------------------------|-----|

| A Novel Learning Based Solution for Efficient Data Transport in Heterogeneous Wireless Networks                 | 402 |

| Scalable Data Collection in Sensor Networks                                                                     | 415 |

| Task Scheduling on Heterogeneous Devices in Parallel Pervasive Systems $(P^2S)$                                 | 427 |

| A Performance Guaranteed Distributed Multicast Algorithm for<br>Long-Lived Directional Communications in WANETs | 439 |

| Session VII: Communication Networks                                                                             |     |

| Maintaining Quality of Service with Dynamic Fault Tolerance in Fat-Trees                                        | 451 |

| Designing a High-Performance Clustered NAS: A Case Study with pNFS over RDMA on InfiniBand                      | 465 |

| Sockets Direct Protocol for Hybrid Network Stacks: A Case Study with iWARP over 10G Ethernet                    | 478 |

| Making a Case for Proactive Flow Control in Optical Circuit-Switched Networks                                   | 491 |

| FBICM: Efficient Congestion Management for High-Performance Networks Using Distributed Deterministic Routing    | 503 |

| Achieving 10Gbps Network Processing: Are We There Yet?                                                          | 518 |

| Session VIII: Architecture                                                                         |     |

|----------------------------------------------------------------------------------------------------|-----|

| SAIL: Self-Adaptive File Reallocation on Hybrid Disk Arrays  Tao Xie and Deepthi Madathil          | 529 |

| Directory-Based Conflict Detection in Hardware Transactional Memory                                | 541 |

| Fault-Tolerant Cache Coherence Protocols for CMPs: Evaluation and Trade-Offs                       | 555 |

| SDRM: Simultaneous Determination of Regions and Function-to-Region Mapping for Scratchpad Memories | 569 |

| An Utilization Driven Framework for Energy Efficient Caches                                        | 583 |

| Author Index                                                                                       | 595 |

# Extreme Computing on the Distributed European Infrastructure for Supercomputing Applications – DEISA

Wolfgang Gentzsch

Distributed European Initiative for Supercomputing Applications, Duke University, USA

**Abstract.** Scientists' dream of accessing any supercomputer in the world, independently from time and space, is currently coming true, to perform even larger and more accurate computer simulations, at their finger tip. Today, high-speed networks transport data at the speed of light, middleware manages distributed computing resources in an intelligent manner, portal technology enable secure, seemless, and remote access to resources, applications, and data, and sophisticated numerical methods approximate the underlying mathematical equations in a highly accurate way. With the convergence of these core technologies into one complex service oriented architecture, we see the rise of large compute and data grids currently being built and deployed by e-Infrastructure initiatives such as DEISA, EGEE, NAREGI, and TERAGRID.

With the aid of one example, in this keynote presentation, we will elaborate on the Distributed European Infrastructure for Supercomputing Applications, DEISA, which recently entered its second phase. We will describe the system architecture, called the DEISA Common Production Environment (DCPE) and the DEISA Extreme Computing Initiative DECI attracting scientists all over Europe to use the networked supercomputing environment, and we will highlight a few impressive success stories from scientists who achieved breakthrough results so far which would not have been possible without such an infrastructure. Finally, we will summarize main lessons learned and provide some useful recommendations.

Biography: Wolfgang Gentzsch is Dissemination Advisor for the DEISA Distributed European Initiative for Supercomputing Applications. He is an adjunct professor of computer science at Duke University in Durham, and a visiting scientist at RENCI Renaissance Computing Institute at UNC Chapel Hill, both in North Carolina. From 2005 to 2007, he was the Chairman of the German D-Grid Initiative. Recently, he was Vice Chair of the e-Infrastructure Reflection Group e-IRG; Area Director of Major Grid Projects of the OGF Open Grid Forum Steering Group; and he is a member of the US President's Council of Advisors for Science and Technology (PCAST-NIT). Before, he was Managing Director of MCNC Grid and Data Center Services in North Carolina; Sun's Senior Director of Grid Computing in Menlo Park, CA; President, CEO, and CTO of start-up companies Genias and Gridware, and professor of mathematics and computer science at the University of Applied Sciences in Regensburg, Germany. Wolfgang Gentzsch studied mathematics and physics at the Technical Universities in Aachen and Darmstadt, Germany.

# Towards Networked Computers: What Can Be Learned from Distributed Computing?

#### David Peleg

Department of Computer Science and Applied Mathematics

The Weizmann Institute of Science, Israel

**Abstract.** The talk will discuss some key ideas and concepts developed by the distributed computing community and examine their potential relevance to the development of networked computers.

**Biography:** David Peleg received the B.A. degree in 1980 from the Technion, Israel, and the Ph.D. degree in 1985 from the Weizmann Institute, Israel, in computer science. He then spent a post-doctoral period at IBM and at Stanford University. In 1988 he joined the Department of Computer Science and Applied Mathematics at The Weizmann Institute of Science, where he holds the Norman D. Cohen Professorial Chair of Computer Sciences. His research interests include distributed network algorithms, fault-tolerant computing, communication network theory, approximation algorithms and graph theory, and he is the author of a book titled "Distributed Computing: A Locality-Sensitive Approach," as well as numerous papers in these areas.

# Computational Environments for Coupling Multiphase Flow, Transport, and Mechanics in Porous Media

Mary F. Wheeler

Center for Subsurface Modeling Institute for Computational Engineering and Sciences The University of Texas at Austin, USA

**Abstract.** Cost-effective management of remediation of contamination sites and carbon sequestration in deep saline aquifers is driving development of a new generation of subsurface simulators. The central challenge is to minimize costs of cleanup and/or maximize economic benefit from an environment whose properties are only poorly known and in which a variety of complex chemical and physical phenomena take place. In order to address this challenge a robust reservoir simulator comprised of coupled programs that together account for multicomponent, multiscale, multiphase flow and transport through porous media and through wells and that incorporate uncertainty and include robust solvers is required. The coupled programs must be able to treat different physical processes occurring simultaneously in different parts of the domain, and for computational accuracy and efficiency, should also accomodate multiple numerical schemes. In addition, this problem solving environment or framework must have parameter estimation and optimal control capabilities. We present a "wish list" for simulator capabilities as well as describe the methodology employed in the IPARS software being developed at The University of Texas at Austin. This work also involves a close cooperation on middleware for multiphysics couplings and interactive steering with Parashar at Rutgers University.

**Biography:** After 24 years at Rice University, Professor Mary Fanett Wheeler, a world-renowned expert in massive parallel-processing, arrived at The University of Texas in the Fall of 1995 with a team of 13 interdisciplinary researchers, including two associate professors, three research scientists, three postdoctoral researchers, and four Ph.D. students. Professor Wheeler is not completely new to UT, however, having received a B.S., B.A., and M.S. degrees from here before transferring to Rice for her Ph.D. under the direction of Henry Rachford and Jim Douglas, Jr. Drs. Rachford and Douglas, both of whom conducted some of the first applied mathematics work in modeling engineering problems, have greatly influenced her career.

With the oil industry's strong presence in Houston, she was at the right place at the right time to advance the leap from theoretical mathematics to practical engineering. She correctly theorized that parallel algorithms would spur a technological revolution, offering a multitude of applications in the fields of bioengineering, pharmaceuticals and population dynamics. Her reputation as a first class researcher has led to several national posts, including serving on the Board of Mathematical Sciences, on the Executive Committee for the NSF's Center for Research on Parallel Computation and in

the National Academy of Engineering. Housed in the Texas Institute for Computational and Applied Mathematics (TICAM) on the UT campus, Professor Wheeler has brought a level of prominence to UT that many believe will bring us into the forefront of applied mathematics.

As Head of UT's new Center for Subsurface Modeling (CSM), which operates as a subsidiary of TICAM, Professor Wheeler and her team focus their computer-based research on finding solutions for societal and environmental dilemmas using computer simulations to help with, among other things, effective reservoir management within the oil and gas industry. Understanding contaminant movement and enhanced oil recovery techniques can save billions of dollars in cleanup as well as production over the next couple of decades. Hazardous waste cleanup is incredibly important to society, she believes, and is an area of study that has only begun to be explored.

Because of the complexity of the problems, Wheeler and her associates must obtain data about the geology, chemistry, and mechanics of a site before they can begin to construct algorithms to accurately depict a simulation. Hence, the interdisciplinary nature of the work, which no one individual within a single department could tackle on his/her own. Yet Professor Wheeler has indeed made great strides toward obtaining expertise in several disciplines key to the success of parallel computing. Indeed, she holds joint appointments in the Departments of Petroleum and Geosystems Engineering, Aerospace Engineering and Engineering Mechanics, and Mathematics. She is also the first woman to hold an endowed Chair in UT's College of Engineering (the Ernest and Virginia Cockrell Chair in Engineering).

Dr. Wheeler's own research interests include numerical solution of partial differential systems with application to the modeling of subsurface and surface flows and parallel computation. Her numerical work includes formulation, analysis and implementation of finite-difference/finite-element discretization schemes for nonlinear coupled pde's as well as domain decomposition iterative solution methods. Her applications include reservoir engineering and contaminant transport in groundwater and bays and estuaries. Current work has emphasized mixed finite-element methods for modeling reactive multi-phase flow and transport in a heterogeneous porous media, with the goal of simulating these systems on parallel computing platforms. Dr. Wheeler has published more than 100 technical papers and edited seven books. She is currently an editor of four technical journals and managing editor of Computational Geosciences. In 1998 she was elected to the National Academy of Engineering.

# The Excitement in Parallel Computing

#### Laxmikant Kale

Department of Computer Science University of Illinois at Urbana-Champaign, USA

**Abstract.** The almost simultaneous emergence of multicore chips and petascale computers presents multidimensional challenges and opportunities for parallel programming. Machines with hundreds of TeraFLOP/S exist now, with at least one having crossed the 1 PetaFLOP/s rubicon. Many machines have over 100,000 processors. The largest planned machine by NSF will be at University of Illinois at Urbana-Champaign by early 2011. At the same time, there are already hundreds of supercomputers with over 1,000 processors each. Adding breadth, multicore processors are starting to get into most desktop computers, and this trend is expected to continue. This era of parallel computing will have a significant impact on the society. Science and engineering will make breakthroughs based on computational modeling, while the broader desktop use has the potential to directly enhance individual productivity and quality of life for everyone. I will review the current state in parallel computing, and then discuss some of the challenges. In particular, I will focus on questions such as: What kind of programming models will prevail? What are some of the required and desired characteristics of such model/s? My answers are based, in part, on my experience with several applications ranging from quantum chemistry, biomolecular simulations, simulation of solid propellant rockets, and computational astronomy.

Biography: Professor Laxmikant (Sanjay) Kale has been working on various aspects of parallel computing, with a focus on enhancing performance and productivity via adaptive runtime systems, and with the belief that only interdisciplinary research involving multiple CSE and other applications can bring back well-honed abstractions into Computer Science that will have a long-term impact on the state-of-art. His collaborations include the widely used Gordon-Bell award winning (SC'2002) biomolecular simulation program NAMD, and other collaborations on computational cosmology, quantum chemistry, rocket simulation, space-time meshes, and other unstructured mesh applications. He takes pride in his group's success in distributing and supporting software embodying his research ideas, including Charm++, Adaptive MPI and the ParFUM framework. Prof. Kale received the B.Tech degree in Electronics Engineering from Benares Hindu University, Varanasi, India in 1977, and a M.E. degree in Computer Science from Indian Institute of Science in Bangalore, India, in 1979. He received a Ph.D. in computer science in from State University of New York, Stony Brook, in 1985.

# Improving Performance of Digest Caches in Network Processors

Girish Chandramohan<sup>1,\*</sup> and Govindarajan Ramaswamy<sup>2</sup>

<sup>1</sup> Akamai Technologies India Pvt. Ltd. <sup>2</sup> Supercomputer Education and Research Centre, Indian Institute of Science, Bangalore 560 012, India gchandra@akamai.com, govind@serc.iisc.ernet.in

**Abstract.** Digest caches have been proposed as an effective method to speed up packet classification in network processors. In this paper, we show that the presence of a large number of small flows and a few large flows in the Internet has an adverse impact on the performance of these digest caches. In the Internet, a few large flows transfer a majority of the packets whereas the contribution of several small flows to the total number of packets transferred is small. In such a scenario, the LRU cache replacement policy, which gives maximum priority to the most recently accessed digest, tends to evict digests belonging to the few large flows. We propose a new cache management algorithm called Saturating Priority (SP) which aims at improving the performance of digest caches in network processors by exploiting the disparity between the number of flows and the number of packets transferred. Our experimental results demonstrate that SP performs better than the widely used LRU cache replacement policy in size constrained caches. Further, we characterize the misses experienced by flow identifiers in digest caches.

#### 1 Introduction

Network applications such as IP forwarding and packet classification involve complex lookup operations. These operations have to be performed at wire speeds and are the bottleneck in achieving faster processing rates in routers [1, 2]. Algorithmic techniques used for packet classification [2, 3] in routers need large tables and require multiple accesses to main memory. Architectural optimizations proposed for speeding up this processing involve caching the data structures used [1, 4, 5] or caching the results of the lookup [6, 7]. Cache based methods exploit temporal locality observed in Internet packets. Consequently, the efficiency of these schemes is dependent on the access characteristics observed in real traces from the Internet. A clear understanding of the cache access patterns is important in order to design a cache management policy for such applications.

Network processors (NPs) [8, 9, 10] have emerged as a viable option to implement network processing applications. The generic architecture of a network

<sup>\*</sup> This study was conducted when the first author was at SERC, IISc.

P. Sadayappan et al. (Eds.): HiPC 2008, LNCS 5374, pp. 6–17, 2008.

<sup>©</sup> Springer-Verlag Berlin Heidelberg 2008

processor consists of a number of simple in-order cores that perform the data plane operations [11]. These cores have support for multiple threads aimed at exploiting packet-level parallelism present in network applications. The cores have small data and instruction caches to speedup network processing applications. These caches are of size 2KB to 8KB typically [8, 9, 11].

In digest caching [7], a fixed, smaller length digest is obtained by hashing the fields used in packet classification. This digest is stored along with the flow class in a cache. Due to reduced the cache entry sizes, a digest cache of a few kilobytes is effective in maintaining a higher hit rate than a result cache.

Previous studies propose maintaining the cache entries with the LRU cache replacement strategy as it performs better than the LFU and probabilistic insertion policies [7]. LRU cache replacement works well in the presence of temporal locality. Internet flows however exhibit distinct characteristics which may be used to obtain higher performance from these constrained caches. In the Internet, a large number of flows have a single packet, whereas a small number of flows have multiple packets and contribute to the majority of the traffic [12]. From a caching perspective, we observe that flows with a single packet do not exhibit any (temporal) locality and hence it is not beneficial to store such entries in the digest cache. More importantly, these single packet flows may evict digests belonging to flows with multiple packets. We propose to exploit this characteristic of Internet flows to improve the performance of a digest cache by using a new cache replacement policy called Saturating Priority (SP). Under the SP cache replacement policy, a new digest entry is inserted in a cache set with the lowest priority. Its priority increases and reaches the maximum priority as more accesses are made to it. During cache replacement, the item with the lowest priority in the set is removed. Such a policy ensures that digests belonging to single packet flows do not replace multiple packet flow digests. We evaluate the miss rate with SP and LRU cache replacement policies using real traces collected from different sites in the Internet. The SP policy outperforms the LRU policy for all traces and cache sizes considered. For a 512-entry 4-way set associative cache, it covers 74% of the gap between LRU cache replacement and an oracle cache replacement policy which places digest entries in the cache only for flows that contain multiple packets.

Further, we characterize the misses incurred by a LRU managed digest cache and show that conflict misses are small compared to capacity and cold misses. This shows that although digest caches can reduce a majority of packet classification lookups, the size of the cache has to be substantially increased in order to reduce the misses to a small fraction.

The rest of the paper is organized as follows. In the next section, we present the necessary background for digest caches. In Sec. 3, we present the characteristics of Internet traffic in terms of flow size distribution and describe our Saturating Priority cache replacement algorithm. Sec. 4 deals with the performance results of the Saturating Priority algorithm. We present the related research proposals in this area in Sec. 5. Finally we conclude in Sec. 6.

#### 2 Background

In this study, we consider a packet classification application [3] in which a tuple consisting of the source IP address and port, destination IP address and port and the protocol field are used to identify packets belonging to a particular network flow. This 5 tuple, called the flow identifier, is used to map the packets of a flow to a particular traffic QoS class. This methodology may also be used in packet forwarding application where the port on which the packet has to be forwarded is stored along with the flow identifier. In network address translation (NAT) application, the digest cache can be used to lookup the address translation information. A digest cache is a generic method for improving the table lookup rate, a commonly used operation in network processing applications.

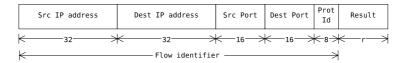

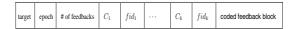

Fig. 1. Result cache entry for packet classification

In case of packet classification for IPv4, result caching involves storing the 104 bit 5-tuple along with the QoS or forwarding information of size r bits as shown in Fig. 1. The memory size required to realize such a cache with sufficiently high hit rate could be large due to the large size of the entries. A recent proposal has been to use a smaller digest of the 5-tuple instead of the actual values in the fields [7].

#### 2.1 Operation of a Digest Cache

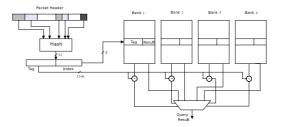

We now describe the operation of the digest cache which was presented by Chang et al. [7]. In case of packet classification, a digest cache works by using a hashing algorithm on the 104-bit 5 tuple to generate a 32-bit hash  $^1$ . The least significant s bits are used to index into a set associative cache of  $2^s$  sets. The remaining (32-s) bits of the hash are used for tag check, after which a cache hit or miss is known. Each cache block stores the r-bit result which is either the classification information or the forwarding information, depending on the application, for which the digest cache is used. Each cache block stores the result of only one tuple as spatial locality is low in these applications. In case of a miss, the processing proceeds by using a full classification algorithm. The digest that missed in the cache replaces another entry in the set using a cache eviction policy that chooses the victim. Steps involved in accessing a digest cache are shown in Fig. 2.

The digest cache acts as a filter, servicing the frequently accessed digests. Only those packets whose digests miss, go through the slower packet classification

<sup>&</sup>lt;sup>1</sup> NPs such as the IXP2400 and IBM PowerNP have a hash unit which may be used to compute the digest.

Fig. 2. Accessing an entry in a 4-way set associative digest cache

algorithm. A higher hit rate in the digest cache is critical for higher classification rates as it decreases the number of packets going through the slower packet classification step [5].

Each entry in the digest cache consists of a tag of (32 - s) bits and r bits of classification information. Thus the total size of a digest cache with  $2^s$  sets and k blocks per set (associativity) is

$$Digest\ Cache\ Size = \frac{((32 - s + r) * 2^s * k)}{8}\ bytes \tag{1}$$

The size of a cache with different number of entries and associativities are shown in Table 1. Here, we assumed that 1 byte IP lookup or classification information is stored along with the digest. This is sufficient for various diff serve classes for which classification has to be performed.

Table 1. Cache sizes for different number of entries and associativities

| Entries | 4-way assoc. | 8-way assoc. |

|---------|--------------|--------------|

| 512     | 2112 bytes   | 2176 bytes   |

| 1024    | 4096 bytes   | 4224 bytes   |

| 2048    | 7936 bytes   | 8192 bytes   |

The IXP 2400 has 2560 bytes of local memory, a 16 entry content accessible memory and a hash unit that may be used to implement a digest cache under software control [8]. The CAM supports LRU replacement. However, we show that using a different cache replacement policy could improve the performance of the cache. The local cache in each processing core of an NP is small, around 2KB. In this study, we consider the performance of digest caches in a network processor environment and consider cache sizes up to 8KB.

### 3 Improving the Performance of Digest Caches

Li et al., [6] evaluate digest caches with different associativities, hash functions and cache management policies. They propose a probabilistic insertion policy

which only partially addresses the problem of the presence of large number of flows. The benefit of this algorithm is comparable to the LRU replacement policy. In fact, the probabilistic replacement policy and LFU replacement policies have a higher miss rate than the LRU cache replacement with two of the edge traces that they considered. On the other hand, we first study the distribution of flow lengths in the Internet and their effect on LRU cache replacement. The number of flows in the Internet, their lengths and rates influences the performance of the digest cache. We then propose SP cache replacement policy which exploits the widely observed disparity in flow sizes to find cache entries for replacement.

#### 3.1 Flow Length Distribution in the Internet

An Internet packet flow is considered active from the time it sends the first packet until it is idle, i.e, it does not send a packet, for 1 second. A similar definition is used in [12]<sup>2</sup>. Flow length is defined as the number of packets sent when a flow is active. The traces from [13] that we use in our study are shown in Table 2. Only Abilene trace has packets that are in both directions<sup>3</sup>. However we show that irrespective of the direction of the flow of packets, there is a disparity in the flow lengths and the number of packets transferred by these flows.

| Trace (Label)                   | Type | Trace Direction | Files                      |

|---------------------------------|------|-----------------|----------------------------|

| Abilene Indianapolis Abilene    | Core |                 | I2K-1091235140-1.erf.gz to |

| router (Abilene)                | Core |                 | I2K-1091308171-2.erf.gz    |

| National Center for Atmospheric | Edge | Unidirectional  | 20031229-223500.gz to      |

| Research (NCAR)                 | Dage | Unidirectional  | 20031229-221000.gz         |

| Front Range Gigapop (FRG)       | Edge | Unidirectional  | FRG-1133754905-1.tsh.gz to |

| 3 311 ( )                       | Duge |                 | FRG-1133818534-1.tsh.gz    |

| Pittsburgh Supercomputing       | Edgo | Unidirectional  | PSC-1145580225-1.tsh.gz to |

| Center (PSC)                    | Euge | Unidirectional  | PSC-1145742328-1.tsh.gz    |

| San Diego Supercomputer Center  | Edge | Linidirectional | SDA-1141865872.erf.gz to   |

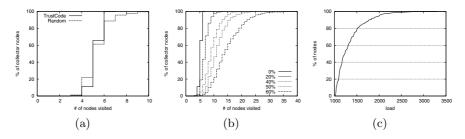

| to Abilene connection (SDA)     | Duge | Unidirectional  | SDA-1142027975.erf.gz      |

**Table 2.** Traces from the Internet used in this study

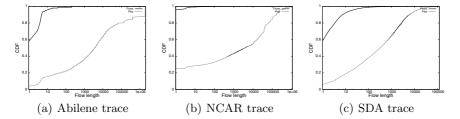

For the three traces, Abilene, NCAR and SDA, Fig. 3 shows the cumulative percentage of flows having packets less than the value on the x-axis. The graph also shows the cumulative percentage of the packets that are transferred by these flows. These traces have 3.1 million, 15.4 million and 4.4 million flows respectively. In NCAR trace, more than 95% of the flows have only a single packet. Abilene and SDA traces have 58% single packet flows. Fig. 3 also shows

<sup>&</sup>lt;sup>2</sup> In [12], the authors use a time out of 60 seconds. Even with a time out of 1 second, there are about 6000 concurrent flows in all our traces. This is more than the number of entries in the digest cache.

<sup>&</sup>lt;sup>3</sup> The packets were merged according to their timestamp to obtain a proper interleaving of the packets as seen by the router.

the cumulative percentage of the traffic (in terms of packets) contributed by flows of different sizes. It can be seen that, irrespective of the direction of the traces, single packet flows, which are a significant part of the total number of flows, contribute less than 6% of the packets transferred in Abilene and SDA traces. In NCAR trace, single packet flows transfer 25% of the total packets. Less than 0.2% of the flows have more than 1000 packets, but they transfer 52% of the packets on an average. Thus Internet traffic exhibits the phenomenon of mass-count disparity [14], i.e. a few important flows transfer a significant number of packets. From the above observations, we see that a large number of flows in the Internet have only a single packet. These flows get entries into the digest cache, but will never be accessed again. Presence of a large number of such flows has a detrimental effect on the performance of the digest cache as they tend to evict the digests of few flows that contain a large number of packets.

Fig. 3. Disparity in the flow lengths and packets transferred

#### 3.2 A New Replacement Algorithm for Digest Caches

The above observations provide an insight into the functioning of the digest cache in a network processor. The cache has to service a large number of flows, but only a small fraction of the flows have multiple packets that are accessed again. From Fig. 3, we infer that the cache replacement policy of a digest cache must strive to retain the digests belonging to large flows within the cache while preventing the single packet flows from occupying entries in the cache.

Given the large number of single packet flows in the Internet and the small cache size, an LRU managed digest cache may suffer from degraded performance due to cache pollution. Previous studies using digest caches used LRU cache replacement strategy as it performed better than LFU and probabilistic insertion policies [6, 7]. LRU cache management gives preference to the most recently accessed entry in the set and puts it in the most-recently-used (MRU) location. In case of network processing applications, the most recently accessed digest usually belongs to a single packet flow and it will never be accessed again. But such digests stay in the cache until they are slowly pushed out by the LRU replacement algorithm. This suggests that LRU may not be the best cache management policy.

In order to overcome this effect, we propose a *Saturating Priority* cache replacement policy that exploits the disparity between the number of flows and

the residency of the digests in the cache. Each entry in a set has a priority that increases each time the entry is accessed, until it reaches a maximum value. Further accesses to the same entry do not increase its priority. Whenever an entry with a lower priority is accessed, it swaps its priority with an entry that has the next higher precedence. A new entry is added to a set with the least priority, after evicting the item with the lowest priority.

|   | Initial<br>State |   |   |   |   |   |   |   |   |

|---|------------------|---|---|---|---|---|---|---|---|

| 4 | а                | 4 | а | 4 | а | 4 | а | 4 | а |

| 3 | b                | 3 | b | 2 | b | 2 | b | 2 | b |

| 2 | с                | 1 | с | 1 | С | 1 | е | 1 | е |

| 1 | d                | 2 | d | 3 | d | 3 | d | 3 | d |

Access Stream: d d e a

Fig. 4. Saturating Priority cache replacement policy

Fig. 4 illustrates the change in priorities of the entries in a 4-way set associative set. The set initially contains the digests marked a,b,c and d. Their priorities are also marked in the figure. Here, a larger number signifies a higher priority. When digest d is accessed two times, it swaps its priority with digests c and d respectively. It thus has a priority of 3. The priority of digests d and d decrease. Digest d now has the lowest priority in the set. As a result, the miss caused by digest d evicts digest d from the cache. The last access in the sequence, access to digest d, does not increase its priority as it has already got the maximum priority.

SP cache replacement evicts any entry that was brought into the cache, but is not subsequently accessed. Entries that are accessed only a few times are likely to be evicted. Also in a digest cache, entries are accessed a number of times when the a flow is active, but the accesses stop when the flows end. The cache replacement policy proactively removes such entries as their priority decreases rapidly.

SP scheme can be implemented in a d way associative cache by maintaining two  $\log_2(d)$  bit pointers per cache entry, which point to cache entries with immediately higher and lower priority. When the priority of an element changes, the pointers in the (at most four) affected cache entries can be updated in parallel.

#### 4 Performance Evaluation

As mentioned in Sec. 1, IP lookup or packet classification is the bottleneck in achieving higher processing rates in routers [1, 2]. By reducing the miss rate of digest caches, higher processing rates can be achieved as the packets are processed from the cache entries instead of the slower off-chip memory. We therefore compare the miss rate of SP scheme with that of the widely used LRU scheme.

In order to understand the maximum improvement in performance of the digest cache that is possible by preventing the detrimental effect of single packet flows, we implemented an oracle cache management policy that inserts a digest into the cache only when it has more than one access in a window of 10,000 accesses in the future. The cache entries are managed with a LRU policy. We call this PRED policy as a simple predictor may be able to predict single packet flows reasonably well.

We consider cache sizes ranging from 2KB to 8KB because as explained in Sec. 1 these are the typical memory sizes available in network processors to implement digest caches. 32-bits from the MD5 hash of the flow identifier is used to obtain the digest. The cache sizes for different configurations are shown in Table 1.

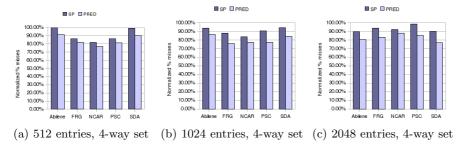

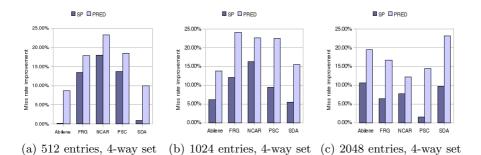

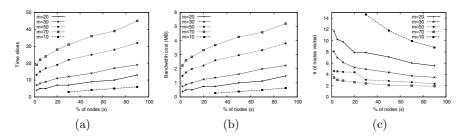

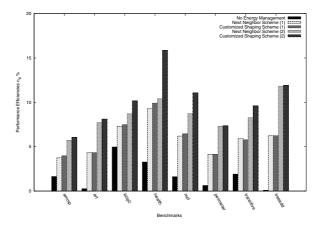

Fig. 5. Normalized misses for a 4-way associative digest cache

For the traces listed in Table 2. Fig. 5 shows the percentage of misses with SP and PRED replacement policies. The misses are normalized wrt. misses incurred with LRU replacement for 4-way set associative caches. The SP policy performs better than the LRU cache replacement policy in terms of miss rates for all 4-way set associative caches. As expected, the PRED cache management policy has lower miss rate than the other two policies.

Table 3 shows the miss rates for LRU and SP policies for 4-way and 8-way associative caches. We see that for almost all the configurations, SP replacement for a 4-way set associative cache has a lower miss rate than LRU replacement for

|       |       | 512 E | ntries |       | 1024 Entries |       |       |       | 2048 Entries |       |       |       |

|-------|-------|-------|--------|-------|--------------|-------|-------|-------|--------------|-------|-------|-------|

| Trace | 4 v   | vay   | 8 v    | vay   | 4 way        |       | 8 way |       | 4 way        |       | 8 way |       |

|       | LRU   |       | LRU    |       | LRU          |       |       |       | LRU          |       | LRU   |       |

|       |       |       |        |       | 29.3%        |       |       |       |              |       |       |       |

| FRG   | 18.6% | 16.1% | 18.2%  | 15.3% | 11.9%        | 10.5% | 11.0% | 9.8%  | 7.4%         | 7.0%  | 6.7%  | 6.7%  |

| NCA.  | 42.1% | 34.5% | 42.1%  | 32.8% | 35.4%        | 29.6% | 34.6% | 28.4% | 29.7%        | 27.3% | 28.6% | 27.2% |

| PSC   | 20.8% | 17.9% | 19.9%  | 16.9% | 13.0%        | 11.8% | 11.8% | 11.1% | 8.2%         | 8.1%  | 7.4%  | 8.1%  |

| SDA   | 49.8% | 49.4% | 49.1%  | 50.0% | 40.2%        | 37.9% | 39.2% | 37.6% | 29.7%        | 26.8% | 28.9% | 25.8% |

**Table 3.** Cache miss rates with SP and LRU policies

a 8-way set associative cache. In SP cache replacement, the maximum priority that an element can get is equal to its set associativity. An element that attains higher priority occupies the cache for a longer duration before it is evicted from the set. As a result, when a flow becomes inactive, it takes longer to be evicted from the cache. This explains the low reduction in miss rate with SP policy for caches with higher associativity.

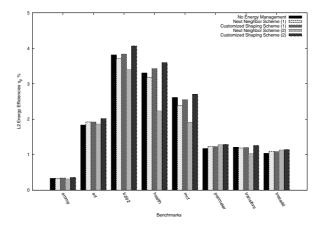

Fig. 6. Miss rate improvement over LRU replacement for 4-way assoc. caches with SP and PRED policies

Fig. 6 shows the improvement in miss rate over LRU scheme for 4-way set associative caches with SP and PRED cache replacement. The NCAR trace shows 18% improvement in miss rate for a 512-entry cache and 8% improvement for a 2048-entry cache. For a 512-entry cache, with the FRG, NCAR and PSC traces, SP covers more than 74% of the gap between the LRU and PRED cache management policy. Even for higher cache sizes, SP covers substantial gap between LRU and PRED replacement. With the PSC trace, SP cache replacement does not show much improvement with large caches, however the miss rate for this trace is already low. For a 512-entry cache with the SDA trace, SP replacement policy has a small improvement over LRU replacement policy. But it has 10% improvement over LRU replacement policy for a 2048-entry cache, covering 41% of the gap between LRU and PRED policies. For 512-entry and 1024-entry caches, SP shows more than 10% miss rate improvement of an average whereas for a 2048-entry cache, the average improvement is 7.08%.

With a 2048-entry cache, the PSC trace with SP cache replacement shows a slightly higher miss rate of 8.1% compared to LRU cache replacement with a miss rate of 7.4%. We observe that with this cache size, the PSC trace has insignificant capacity misses (refer Fig. 7). In this case, the SP cache replacement policy that evicts the most recently accessed digests incurs slightly higher misses as the digests are removed before their priority can increase. But with smaller caches such as those seen in NPs, SP policy has lower miss rate than LRU cache replacement.

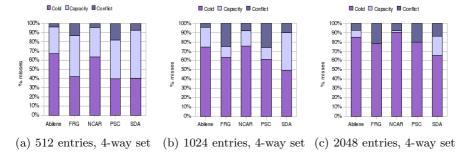

We see that the Abilene, NCAR and SDA traces suffer more than 13% miss rate even for a 2048-entry cache with LRU cache replacement. In order to understand the reason for this, we classified the misses in a LRU managed cache as

cold, capacity and conflict misses. Misses due to accesses that were not present in a window of previous 10,000 accesses are classified as cold misses. We used this definition of cold misses because when network flows stop, their digests are evicted from the cache. When a packet with the same digest is seen next, it is considered a new flow. Accesses to digests that are present in the window of previous 10,000 accesses but not in a fully associative cache are classified as capacity misses. Conflict misses are those which occur when a set associative cache is used instead of a fully associative cache of the same size.

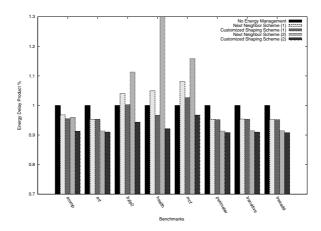

Fig. 7. Types of misses in digest caches

Conflict misses may be reduced by using a better cache placement and management policy. From Fig. 7 we observe that for a 1024-entry, 4-way set associative digest cache less than 10% of the misses are due to cache conflicts in case of Abilene, NCAR and SDA traces. Traces that already have a high hit rate, such as FRG and PSC, have about 25% conflict misses. This observation shows that the cold and capacity misses dominate the misses in a digest cache. As expected, for larger caches, the ratio of capacity misses decreases but the number of cold misses does not decrease. This is mainly because of the large number of small flows (refer Fig. 3). As a result, continuously increasing the cache size leads to small improvements in performance. Instead, it may be worthwhile to use better algorithmic or data structure caching approaches to improve the hit rate.

#### 5 Related Work

Zhang et al. [12] use traces from different locations in the core and edge of the Internet to study the characteristics of Internet traffic flows. Disparity in the flow lengths is shown to be more drastic than the disparity in the rate of the flows. They also show that there is a correlation between the size of the flow and its rate. This disparity in the number of packets present in a few flows inspired us to propose a new cache management scheme for digest caches.

Feitelson [14] proposed metrics to quantify mass-count disparity, a phenomenon seen in a number of computer applications such as network traffic, job time distribution in operating systems, file size distribution. In [15], Feitelson et al. use the same phenomenon to design a filter for identifying and retaining common addresses in a direct mapped cache L1 cache of a superscalar processor. Since a few addresses are accessed a large number of times, the authors show that a randomly chosen reference to the cache belongs to an address that is accessed many times.

Mudigonda et al. [4] propose the use of caches for data structures used in network processing applications as it benefits a large number of such programs. Similarly, Gopalan et al. [5], propose an intelligent mapping scheme to reduce conflict misses in IP lookup data structure caches and to enable frequent updates of the routing table. On the other hand, we exploit the traffic patterns observed in real traces to improve the effectiveness of small digest caches for packet classification application. The insight gained from the traffic patterns can also be applied to data structure caches. We leave this to future work.

Qureshi et al. [16] propose a LRU insertion policy (LIP) for L2 caches in general purpose processors which, like SP, inserts the cache lines in the least recently used location in the set instead of the MRU location. Lines are moved to the MRU location in case they are accessed in the LRU location whereas the SP policy allows the cache entries to slowly percolate to the MRU position. LIP is aimed at applications that have a larger working set than the cache size. For applications that have a cyclic reference pattern, it prevents thrashing of the cache by retaining some entries in the cache so that they contribute to cache hits. On the other hand, we observe that the large disparity in the flow sizes in the internet leads to poor performance of LRU managed result caches in network applications. In SP, the priorities are managed such that cache replacement policy can recognize digests belonging to large flows.

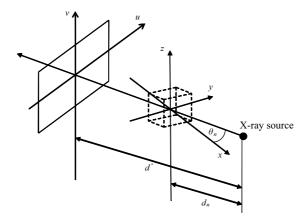

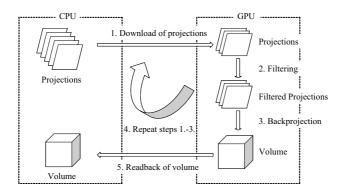

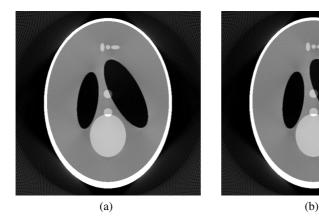

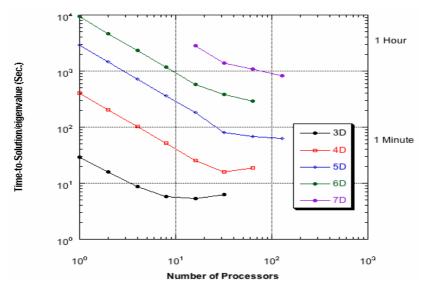

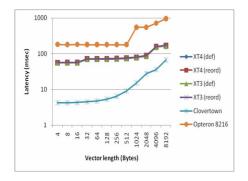

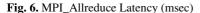

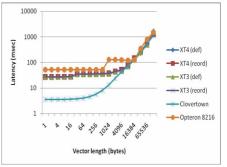

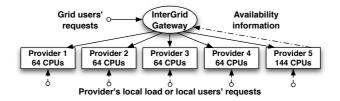

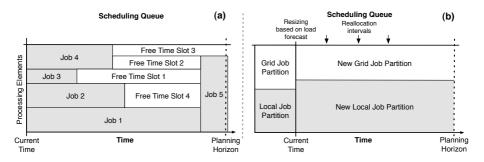

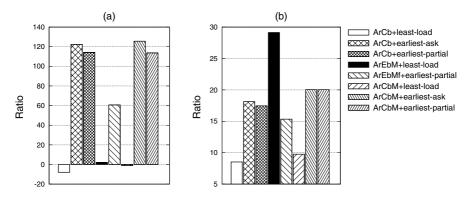

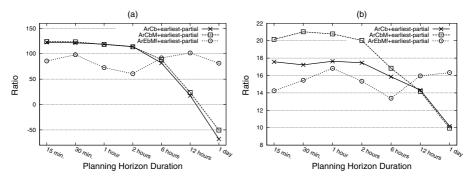

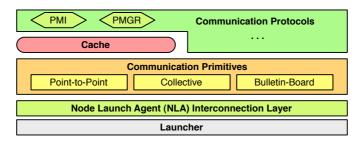

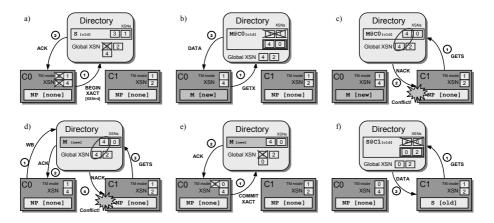

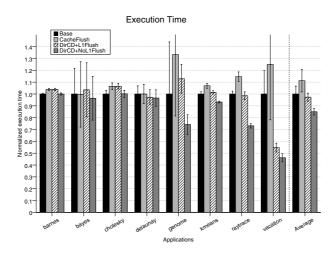

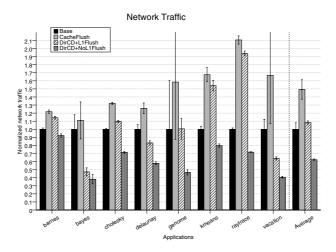

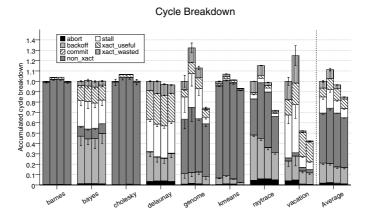

#### 6 Conclusions